2007년은 윌리엄 쇼클리와 존 바딘, 발터 브래타인에 의해 최초의 트랜지스터가 만들어진 지 60년이 되는 해이다. 보청기를 시작으로 상업용 제품에 사용되기 시작한 트랜지스터는 최초의 트랜지스터 라디오에 4개의 게르마늄 트랜지스터가 내장되는 것을 시작으로 로버트 노이스가 최초의 특허를 받으며 집적회로로 발전하기 시작했다.

1965년, 인텔의 고든 무어는 일렉트로닉스 매거진에 기고한 글에서 미래에는 칩 하나에 탑재되는 트랜지스터의 수가 매 2년마다 두 배씩 증가하게 될 것이라 예측하면서 그 유명한 무어의 법칙이 탄생하게 된다. 이후 인텔은 트랜지스터의 집적에 있어 현재까지 무어의 법칙을 지켜오고 있는데, 1971년 인텔 최초의 마이크로 프로세서인 4004에 2,000개 가량의 트랜지스터를 집적한 이래 펜린에 이르러 마침내 8억 개 이상의 트랜지스터를 집적하게 되었다. 우리 기억 속에 남아있는 386 프로세서는 약 27만개, 최초의 펜티엄 프로세서에는 약 3백만 개의 트랜지스터가 집적되어 있다.

그렇다면 '펜린'에서 구현된 45nm란 도대체 어느 정도의 두께일까? 수학적으로야 간단히 풀이될 수 있겠지만, 정작 그것이 얼마나 가느다란 회선인지는 좀처럼 이해하기 쉽지 않다. 아마도 우리의 눈으로 볼 수 있는 범주를 훨씬 벗어나버린 영역에 존재하는 단위를 피부로 느끼기 어렵기 때문이 아닐까 생각된다.

1947년, 벨 연구소에서 개발된 최초의 트랜지스터는 사람의 손바닥 위에 올라갈만한 크기였다. 이후 하나의 회로에 집적되기 시작하며 그 크기도 작아지기 시작해 현재엔 인간의 눈으로 볼 수 없는 영역으로 발전했다. 인텔은 향후 등장할 32nm 기반 칩셋을 이미 시연했고, 최근 삼성은 40nm 기반의 플래시 메모리를 선보였다.

1947년, 벨 연구소에서 개발된 최초의 트랜지스터는 사람의 손바닥 위에 올라갈만한 크기였다. 이후 하나의 회로에 집적되기 시작하며 그 크기도 작아지기 시작해 현재엔 인간의 눈으로 볼 수 없는 영역으로 발전했다. 인텔은 향후 등장할 32nm 기반 칩셋을 이미 시연했고, 최근 삼성은 40nm 기반의 플래시 메모리를 선보였다.

45nm 기반의 프로세서가 만들어 졌다는 의미는 45nm 만한 트랜지스터가 만들어 졌다는 의미와 동일하게 볼 수 있는데, 산술적으로 보자면 1m를 10억 개로 나눈 두께라 할 수 있다. 머리카락 한 올의 폭에 약 2,000개의 트랜지스터를 넣을 수 있는 크기이며, 인간의 적혈구 표면에 약 400개를 채워 넣을 수 있는 크기이다.

인텔의 새로운 '펜린' 프로세서는 바로 이러한 트랜지스터 8억 2천만 개(쿼드 코어)가 집적된다. 하지만 극도로 미세해진 45nm 공정 덕분에 다이의 크기는 107㎟(듀얼 코어)으로 오히려 25% 줄어들게 되었다. 더욱이 반가운 점은 새로운 쿼드 코어 프로세서도 인텔의 65nm 기반 듀얼 코어 프로세서보다 오히려 적은 전력만으로 동작하게 되었다는 점일 것이다.

인텔의 45nm 프로세서가 만들어질 수 있던 가장 주요한 기술로 High-K 기술을 들 수 있는데, 인텔의 공동 창업자이며, 무어의 법칙을 만들어낸 고든 무어는 "하이-케이 및 메탈 소재의 적용은 1960년대 후반 폴리 실리콘 게이트 MOS 트랜지스터가 출시된 이래 이뤄진 트랜지스터 기술의 여러 변화 중 가장 괄목할만한 일"이라 평하고 있다.

|

|

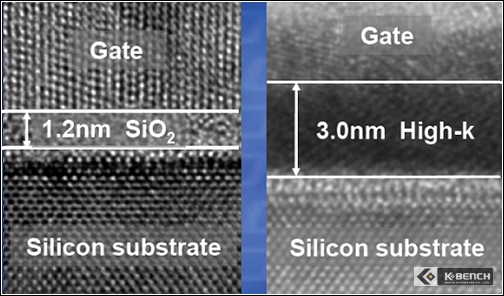

▲ High-K / Metal Gate |

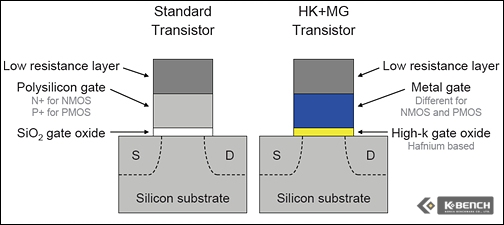

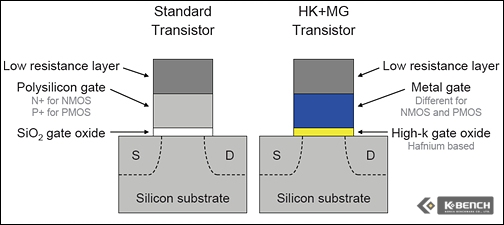

실리콘 다이옥사이드(Silicon Dioxide)는 제조상의 편의성과 지속적인 트랜지스터의 성능 증진 능력 때문에 점점 더 가느다란 형태로 변형되어 40년이 넘게 트랜지스터 게이트 절연체에 사용되어 오고 있다. 트랜지스터가 디지털로 전송되는 신호 0과 1을 처리하는 작은 스위치라 본다면, 이 두 가지 신호를 위해 트랜지스터를 빠르게 켜고 끌 수 있어야 한다. 게이트란 이때 트랜지스터를 켜고 끄는 스위치와 같은 역할을 하게 되며, 게이트 절연체는 게이트 아래에 있는 단열재로써 전류가 흐르는 채널과 게이트를 분리시켜주는 역할을 하게 된다.

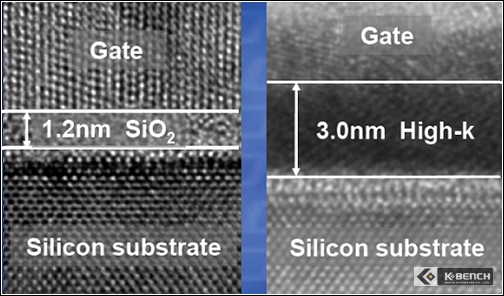

위 그림의 좌측은 기존 실리콘 다이옥사이드 게이트 절연체를 보여주고 있는데, 인텔은 최근의 제품에서 1.2nm 두께까지 이를 성공적으로 축소시켜 왔다. 문제는 이러한 지속적인 축소가 결국 절연체를 통한 누출 전력을 증가시켰고, 결과적으로 이것이 불필요한 전력의 소모 및 열의 발생으로 이어져왔다는 점일 것이다. 때문에 업계에서는 실리콘 다이옥사이드 게이트 절연체의 얇은 두께와 관련된 트랜지스터 게이트 전류의 누출을 무어의 법칙이 직면한 가장 어려운 문제점으로 여겨왔다.

이 문제를 해결하기 위해 조금 더 두꺼운 하프늄 기반의 High-K 소재로 이를 변경한 것이 이번 45nm 프로세서의 주된 특징이라 할 수 있는데, 이 절연체는 현재 사용되는 실리콘 게이트 전극과는 호환되지 않으므로 새로운 메탈 게이트 소재를 함께 개발해 적용하고 있는 것으로 알려지고 있지만 인텔은 아직까지 이에 대한 정보는 밝히지 않고 있다.

이러한 구조적 특성은 45nm로 미세화된 트랜지스터와 함께 맞물려 훨씬 긍정적인 효과들을 가져오게 되는데, 인텔의 주장에 따르면 기존 실리콘 다이옥사이드와 비교할 때 무려 10배 가량 전력의 누출 양이 감소했다고 한다. 반대로 드라이브 전류량은 오히려 증가하게 되는데, 인텔의 자료에 따르면 드라이브 전류량은 20% 증가하게 되며, 결과적으로 대단히 뛰어난 트랜지스터의 동작 특성을 얻게 된다.

또 45nm 트랜지스터는 이전세대의 제품들보다 크기가 작기 때문에 이를 켜고 끄는데 소요되는 전력 역시 30% 가량 감소하게 된다. 트랜지스터가 사용하는 전력 량을 줄이고, 누설되는 전류를 차단해 온전하게 공급함으로써 프로세서의 동작에 필요한 전력량을 줄임과 동시에 더 우수한 동작 특성을 확보하게 되는 것이다.

|

|

▲ High-K / Metal Gate 구조 |

결과적으로 '펜린'에 탑재된 45nm 트랜지스터는 1초에 약 3천억 번 켜고 끌 수 있게 되었다. 1초면 지구를 7바퀴 이상 도는 엄청난 빛의 속도도 이 트랜지스터가 한 번 켜졌다 꺼지는 동안 0.25cm를 나아갈 수 없다고 한다면 조금은 이해가 쉬울까?

인텔의 자료에 따르면 소스-드레인 누출량은 다섯 배 이상 감소, 드라이브 전류량은 20% 증가, 그리고 앞서 언급했듯 절연체를 통한 누출은 10배 가량 감소했다고 한다. 눈으로 확인할 수 없는 부분이기 때문에 인텔의 자료에서 나타나는 수치들이 다소 과장됐을 가능성을 배제할 순 없겠지만, 현 시점에서 45nm 공정을 제품의 생산에 연결시킨 것 만으로도 그들의 공정 기술이 가장 앞서가고 있다는 것은 부정할 수 없어 보인다.